已绑定手机 已绑定手机

|

1.外围电路

1.1 DVP 接口

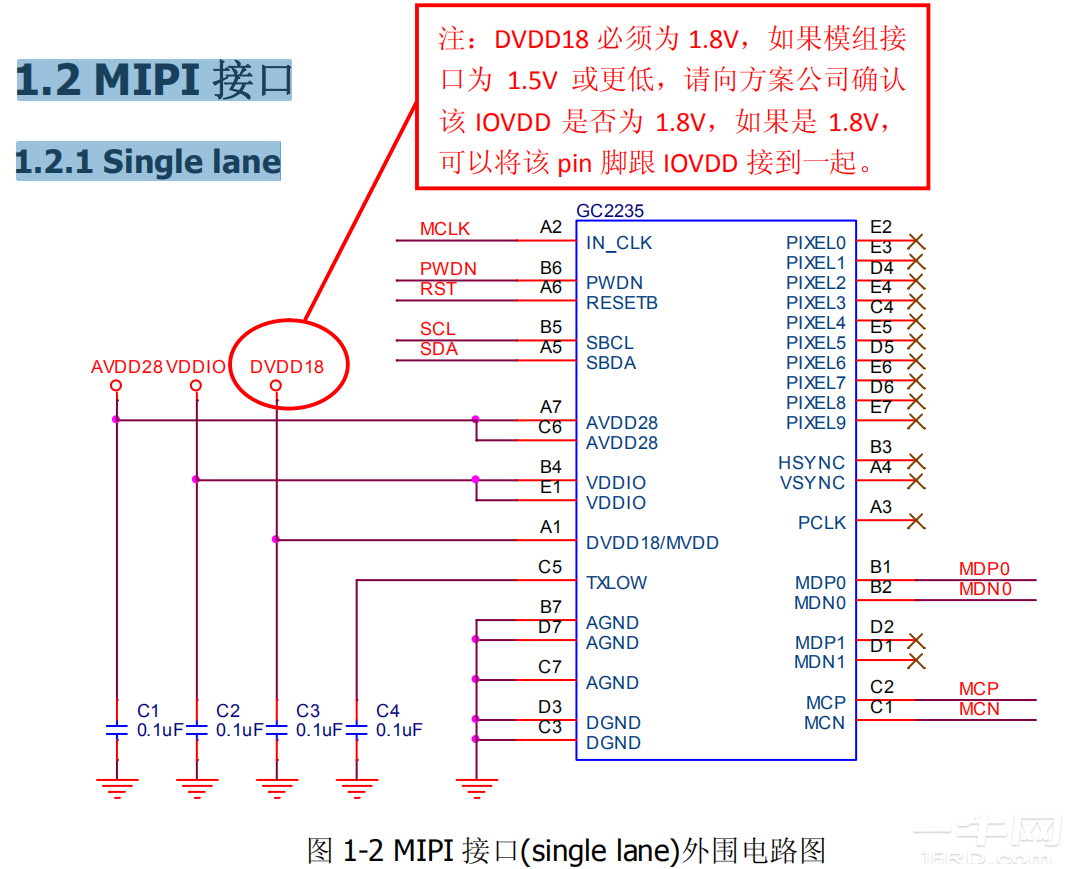

1.2 MIPI 接口

1.2.1 Single lane

2.设计说明

2.1 外围电路设计说明

GC2235芯片有三路电源供电:AVDD28、DVDD18(MVDD)、IOVDD。

AVDD28为2.8V供电电源,2.7~3.0V;

DVDD18(MVDD)为数字电路供电电源,1.7~1.9V;

IOVDD为I/O电源,1.7~3.0V;

靠近电源处,加如图示C1、C2、C3、C4滤波电容,容值为0.1μF;如果平台接口能接10bit数据的,请将10bit数据全部接出;如果平台接口是接8bit数据的,请引出D<9>~D<2>。

DVDD18(MVDD)外接电压必须为1.7~1.9V,如模组接口DVDD供电为1.5V或1.2V时,需跟方案公司确认IOVDD是否为1.8V,如果是可以将DVDD18(MVDD)跟IOVDD接到一起,以保证电压满足芯片工作要求。

如果客户端MIPI接口支持两条lane,建议将芯片的两条lane都引出来;

电容摆放应尽量靠近电源Pin脚;

所有电容均不可省去,否则会影响图像质量;

所有的GND线,需要在内部接到一起之后,再做铺铜,否则会影响信号质量;

电源线、GND走线宽度至少加粗至0.2mm以上;

芯片有RESET pin,需要引出控制;

FPC/PCB布线时尽量让SBDA/SBCL线远离高速的信号线(如PCLK/D0~D2);

SBCL/SBDA pin 外部需要4.7k~10kΩ的上拉电阻;

MCP、MCN需要尽量平行走线,等长;尽量少打或不打过孔;且要远离高频信号线(如MCLK),最好是能用地线保护起来,且差分线对走线的背面也尽量是地线走线,并铺地铜作为参考层。差分线对的匹配阻抗要求为100Ω±10%。

MDP、MDN需要尽量平行走线,等长;尽量少打或不打过孔;且要远离高频信号线(如MCLK),最好是能用地线保护起来,且走线的背面也尽量是地线走线,并铺地铜作为参考层。差分线对的匹配阻抗要求为100Ω±10%。

3. GC2235 CSP 封装说明

3.1 GC2235 CSP 封装(单位:μm)

3.4 PCB 焊盘设计说明

注:Sensor 封装锡球大小为 260μm。

格科微GC2235模组设计指南:回复下载附件

|

|