一般说明

854S01I 是一款高性能 2:1 差分转 LVDS 多路复用器。 854S01I 还可以执行差分转换,因为差分输入接受 LVPECL、LVDS 或 CML 电平。854S01I 采用小型 3mm x 3mm 16 VFQFPN 封装,非常适合在空间受限的电路板上使用。

特征

• 2:1 LVDS 多路复用器

• 一对 LVDS 输出

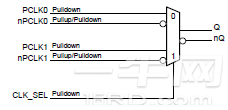

• 两个差分时钟输入可以接受:LVPECL、LVDS、CML

• 最大输入/输出频率:2.5GHz

• 通过使用 nPCLK0、nPCLK1 上的电阻偏置网络将 LVCMOS/LVTTL 输入信号转换为 LVDS 电平

• RMS 附加相位抖动:0.06ps(典型值)

• 传播延迟:600ps(最大值)

• 部件间偏移:350ps(最大值)

• 全3.3V 供电模式

• -40°C 至 85°C 环境工作温度

• 支持高达 +105°C 的外壳温度

• 提供无铅 (RoHS 6) 封装

框图

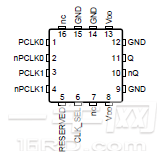

引脚分配

854S01I 16 引脚 VFQFPN 3mm x 3mm x 0.925mm 封装体 K包 顶视图

854S01I

16 引脚 VFQFPN

3mm * 3mm * 0.925mm 封装体

K包

顶视图

表 1. 引脚说明| Number | Name | Type | Description | | 1 | PCLK0 | Input | Pulldown | 同相差分时钟输入。 | | 2 | nPCLK0 | Input | Pullup/ Pulldown | 反相差分时钟输入。 悬空时默认为 VDD/2。 | | 3 | PCLK1 | Input | Pulldown | 同相差分时钟输入。 | | 4 | nPCLK1 | Input | Pullup/ Pulldown | 反相差分时钟输入。 悬空时默认为 VDD/2。 | | 5 | RESERVED | Reserve |

| 预留引脚。 | | 6 | CLK_SEL | Input | Pulldown | 时钟选择输入。 高电平时,选择 PCLK1、nPCLK1 输入。 低电平时,选择 PCLK0、nPCLK0 输入。 LVCMOS/LVTTL 接口电平。 | | 7, 16 | nc | Unused |

| 没有连接。 | | 8, 13 | VDD | Power |

| 电源引脚。 | | 9, 12, 14, 15 | GND | Power |

| 电源地。 | | 10, 11 | nQ, Q | Output |

| 差分输出对。 LVDS 接口电平。 |

注意:上拉和下拉是指内部输入电阻。 有关典型值,请参见表 2,引脚特性

表 2. 引脚特性| Symbol | Parameter | Test Conditions | Minimum | Typical | Maximum | Units | | CIN | Input Capacitance |

|

| 2 |

| pF | | RPULLUP | Input Pullup Resistor |

|

| 37 |

| kΩ | | RPULLDOWN | Input Pulldown Resistor |

|

| 37 |

| kΩ |

功能表

表 3. 控制输入功能表

| CLK_SEL | PCLK Selected | | 0 | PCLK0, nPCLK0 | | 1 | PCLK1, nPCLK1 |

绝对最大额定值

注意:超出绝对最大额定值下所列的应力可能会对设备造成永久性损坏。

这些额定值仅是应力规格。 不暗示产品在这些条件或超出直流特性或交流特性中所列条件的任何条件下的功能操作。 长时间暴露在绝对最大额定值条件下可能会影响产品可靠性。

| Item | Rating | | Supply Voltage, VDD | 4.6V | | Inputs, VI | -0.5V to VDD + 0.5V | | Outputs, IO Continuous Current Surge Current | 10mA

15mA | | Package Thermal Impedance, JA | 74.7℃/W (0 mps) | | Storage Temperature, TSTG | -65℃ to 150℃ |

更多内容请查看附件

|