9FGL02x1/04x1/06x1/08x1D器件包括一个3.3V PCIe Gen1-5时钟发生器系列。有2、4、6和8个输出版本,每个差分输出有一个专门的OE#引脚,支持PCIe CLKREQ#功能。

PCIe 时钟架构

▪ 通用时钟 (CC)

▪ 带和不带扩频的独立参考 (IR) (SRIS, SRNS)

应用

▪ 服务器/高性能计算

▪ nVME 存储

▪ 网络

▪ 加速器

▪ 工业控制

输出功能

▪ 2、4、6 或 8 对 100MHz PCIe 输出对

▪ 一个 3.3V LVCMOS REF 输出,支持网络唤醒 (WOL)

▪ 请参阅 AN-891 以轻松交流耦合到其他逻辑系列

主要规格

▪ 90fs RMS 典型抖动(PCIe Gen5 CC)

▪ < 50ps 差分输出的周期到周期抖动

▪ < 50ps 差分输出的输出到输出偏移

▪ 差分输出上的 ±0ppm 合成误差

特征

▪ 100Ω 和 85Ω 系统的集成终端为每个输出节省 4 个电阻

▪ 112–206 mW 典型功耗(3.3V 时)

▪ VDDIO 轨允许在可选的情况下节省 35% 的功率

1.05V(仅限 9FGL06 和 9FGL08)

▪ 设备包含默认配置;不需要 SMBus

▪ SMBus 可选功能允许针对客户要求进行优化:

• 输入极性和上拉/下拉

• 输出压摆率和幅度

• 每个输出阻抗(85Ω 或 100Ω)

输出

▪ 联系工厂定制默认配置

▪ 25MHz 输入频率

▪ OE# 管脚支持 PCIe CLKREQ# 功能

▪ 引脚可选 SRnS 0%、CC 0% 和 CC/SRIS -0.5% 扩展

▪ SMBus 可选 CC/SRIS -0.25% 扩展

▪ CC/SRIS 扩展设置之间的干净切换

▪ DIF 输出被阻塞,直到 PLL 被锁定;清洁系统启动

▪ 2 个可选 SMBus 地址

▪ 节省空间的包:

• 4 * 4 毫米 24-VFQFPN (9FGL02x1D)

• 5 * 5 毫米 32-VFQFPN (9FGL04x1D)

• 5 * 5 毫米 40-VFQFPN (9FGL06x1D)

• 6 * 6 毫米 48-VFQFPN (9FGL08x1D)

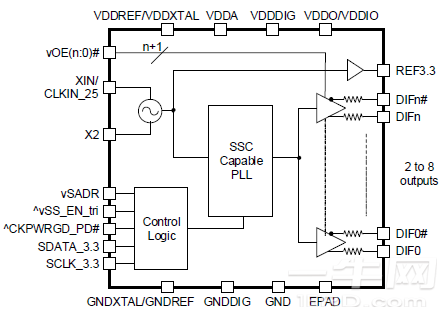

图1.框图

图1.框图

1. 引脚信息

1.1 9FGL02x1D 引脚分配

图2.4 × 4 mm 24-VFQFPN封装 - 俯视图

图2. 4 × 4 mm 24-VFQFPN封装 - 俯视图

1.2 9FGL04x1D引脚分配

图3. 5 × 5 mm 32-VFQFPN封装 - 俯视图

1.3 9FGL06x1D引脚分配

图4. 5 × 5 mm 40-VFQFPN封装 - 俯视图

图4. 5 × 5 mm 40-VFQFPN封装 - 俯视图

更多内容请查看附件

|