CertusPro™-NX系列的低功耗通用FPGA具有10G SerDes、LPDDR4存储器接口支持和高达100k的逻辑单元,可用于多个市场的广泛应用。它建立在莱迪思nexus FPGA平台上,采用低功耗的28纳米FD-SOI技术。它结合了FPGA的极端灵活性和FD-SOI技术的低功耗和高可靠性(由于极低的SER),并提供小尺寸封装选项以及0.8和1.0毫米球距封装选项。

CertusPro-NX支持各种接口,包括PCI Express®(Gen1、Gen2和Gen3)、以太网(最高10G)、SLVS-EC、CoaXPress、eDP/DP、LVDS、Generic 8b10b、LVCMOS(0.9-3.3 V)等等。

CertusPro-NX的处理功能包括多达10万个逻辑单元,156个乘法器(18*18),7.3 Mb的嵌入式存储器(由EBR和LRAM块组成),分布式存储器和DRAM接口(支持DDR3、DDR3L、LPDDR2和LPDDR4,最高1066 Mbps *64bit数据宽度)。

CertusPro-NX FPGA支持对基于SRAM的可重构逻辑结构的快速配置,对其可编程sysI/O™的超快速配置以及TransFR™现场升级功能。还支持设计安全特性,如AES-256加密和ECDSA验证。除了FD-SOI技术固有的高可靠性(由于其极低的SER),CertusPro-NX器件还支持主动可靠性功能,如内置基于帧的软错误检测(SED)/软错误纠正(SEC)(用于基于SRAM的逻辑结构),以及ECC(用于EBR和LRAM)。双1 MSPS 12位模数转换器(ADC)可用于系统监控功能的片上。

莱迪思Radiant™设计软件允许大型复杂的用户设计在CertusPro-NX FPGA系列中有效实现。CertusPro-NX器件的合成库支持可用于流行的逻辑综合工具。Radiant工具使用合成工具的输出以及来自其楼层规划工具的约束,在CertusPro-NX器件中放置和布线用户设计。这些工具从路由中提取时序,并将其回注到设计中进行时序验证。

莱迪思为CertusPro-NX系列提供了许多预设计的知识产权(IP)模块。通过使用这些可配置的软IP核作为标准化块,您可以自由地专注于您设计的独特方面,提高您的生产力。

1.1. 特征

可编程架构

50k 到 100k 逻辑单元

sysDSP™ 模块中的 96 至 156 个乘法器 (18 * 18)

3.8 到 7.3 Mb 的嵌入式内存(包括 EBR 和 LRAM)

170 到 299 个可编程 sysI/O(高性能和宽范围 I/O)

可编程 sysI/O,旨在支持各种接口

底部 I/O bank 支持高性能 (HP) I/O

支持高达 1.8 V VCCIO

混合电压支持(1.0 V、1.2 V、1.5 V 和 1.8 V)

高达 1.5 Gbps 的高速差分

支持 LVDS、Soft D-PHY 发射器 (Tx)/接收器 (Rx)、LVDS 7:1 Tx/Rx、SLVS Tx/Rx、subLVDS Rx

支持 SGMII(千兆以太网):

1.25 Gbps 的两个通道 (Tx/Rx)

专用 DDR3/DDR3L 和 LPDDR2/LPDDR3/LPDDR4 内存支持 DQS 逻辑,高达 1066 Mbps 数据速率和 * 64 位数据宽度

左侧、右侧和顶部 I/O Bank 支持宽范围 (WR) I/O

支持高达 3.3 V VCCIO

混合电压支持:1.2 V、1.5 V、1.8 V、2.5 V 和 3.3 V

可编程转换率:慢速、中速和快速

受控阻抗模式

模拟 LVDS 支持

热插拔支持

嵌入式 SerDes

每通道 625 Mbps 到 10.3125 Gbps,最多 8 个通道

多协议 PCS 支持

PCIe 硬 IP 支持:

第一代、第二代和第三代

端点和根复合体

多功能多达四个功能

最多四个车道

以太网

10GBASE-R,10.3125 Gbps

1.25 Gbps 和 2.5 Gbps 的 SGMII

每通道 3.125 Gbps 的 XAUI

1.25 Gbps、2.5 Gbps 和 5 Gbps 的 SLVS-EC

1.62 Gbps (RBR)、2.7 Gbps (HBR)、5.4 Gbps (HBR2) 和 8.1 Gbps (HBR3) 的 DP/eDP

1.25 Gbps、2.5 Gbps、3.125 Gbps、5 Gbps 和 6.25 Gbps 的 CoaXPress

多种数据速率的通用 8b10b

SerDes-only 模式允许直接 8 位或 10 位接口到 FPGA 逻辑

电源模式——低功耗模式和高性能模式

用户可选

用于节能和/或散热挑战的低功耗模式

用于更快处理的高性能模式

小尺寸封装选项

9 mm * 9 mm 至 27 mm * 27 mm 封装尺寸

两个高达 1.25 Gbps 的时钟数据恢复 (CDR) 通道,以支持 HP I/O 上的 SGMII

Rx 的 CDR

8b/10b 解码

每个 CDR 块的独立失锁 (LOL) 检测器

sysCLOCK™ 模拟 PLL

3 个在 50k LC 中,4 个在 100k LC 中

每个 PLL 六个输出

小数 N

可编程和动态相位控制

支持扩频时钟

sysDSP 增强型 DSP 模块

强化预加器

AI/ML 支持的动态转换

四个 18 * 18、八个 9 * 9、两个 18 * 36 或 36 * 36 乘法器

每个 sysDSP 块高级 18 * 36、两个 18 * 18 或四个 8 * 8 MAC

提供高达 3.7 Mb 的 sysMEM™ 嵌入式块 RAM (EBR)

可编程宽度

纠错编码 (ECC)*

先进先出(FIFO)

344 kbits 至 639 kbits 分布式 RAM

大型 RAM 块

每块 0.5 Mbits

每个设备最多七个(总共 3.5 Mbit)

内部总线接口支持

APB 控制总线

用于数据总线的 AHB-Lite

AXI4 流

配置 – 快速、安全

SPI – ×1、×2、×4 高达 150 MHz

主从 SPI 支持

JTAG

I2C 和 I3C

支持即时启动的超快 I/O 配置(使用 Early I/O release 功能)

LFCPNX-100 设备的完整设备配置不到 30 毫秒

密码引擎

比特流加密——使用 AES-256

比特流认证——使用 ECDSA

散列算法 – SHA、HMAC

真随机数发生器

AES 128/256 加密

单粒子干扰 (SEU) 缓解支持

由于 FD-SOI 技术,软错误率 (SER) 极低

软错误检测——嵌入式硬宏

软错误纠正——对用户设计操作透明

软错误注入——模拟 SEU 事件来调试系统错误处理

双 ADC – 1 MSPS、12 位逐次逼近寄存器 (SAR),具有同步采样*

三个连续时间比较器

系统级支持

符合 IEEE 1149.1 和 IEEE 1532 标准

显示逻辑分析仪

用于设备初始化和一般用途的片上振荡器

1.0 V 核心电源

*提供商业/工业 –8 和 –9 速度等级以及汽车 –7 和 –8 速度等级。

表 1.1。 CertusPro-NX 系列选择指南

| Device | LFCPNX-50 | LFCPNX-100 | | Logic Cells1 | 52k | 96k | | Embedded Memory (EBR) Blocks (18 kb) | 96 | 208 | | Embedded Memory (EBR) Bits (kb) | 1,728 | 3,744 | | Distributed RAM Bits (kb) | 344 | 639 | | Large Memory (LRAM) Blocks (512 kb) | 4 | 7 | | Large Memory (LRAM) Bits (kb) | 2,048 | 3,584 | | 18 X 18 Multipliers | 96 | 156 | | ADC Blocks3 | 2 | 2 | | 450 MHz High Frequency Oscillator | 1 | 1 | | 32 kHz Low Power Oscillator | 1 | 1 | | GPLL | 3 | 4 | | PCIe Gen3 hard IP | 1 | 1 | | SerDes(Quad/Channels) | 1/4 | 2/82 | | Packages (Size, Ball Pitch) | SerDes Channels/I/O (Wide Range (WR) GPIO (Top/Left/Right Banks) + High Performance (HP) GPIO (Bottom Banks) + ADC dedicated inputs) | | ASG256 (9 mm * 9 mm, 0.5 mm) | 4/163 (73 + 84 + 6) | 4/165 (75 + 84 + 6) | | CBG256 (14 mm * 14 mm, 0.8 mm) | 4/163 (73 + 84 + 6) | 4/165 (75 + 84 + 6) | | BBG484 (19 mm * 19 mm, 0.8 mm) | 4/269 (167 + 96 + 6) | 8/305 (167 + 132 + 6) | | BFG484 (23 mm * 23 mm, 1.0 mm) | 4/269 (167 + 96 + 6)5 | 4/305 (167 + 132 + 6)5 | | LFG672 (27 mm * 27 mm, 1.0 mm) | — | 8/305 (167 + 132 + 6)5 |

笔记:

1. 逻辑单元 = LUT * 1.2 有效性。

2. 一些套餐只有一个四路和四个通道。

3. 提供商业/工业 –8 和 –9 速度等级以及汽车 –7 和 –8 速度等级。

4. 对于LFCPNX-100,Hard IP 的PCIe Link Layer 仅适用于QUAD0。

5. 仅适用于商业和工业温度等级。

2. 架构

2.1. 概述

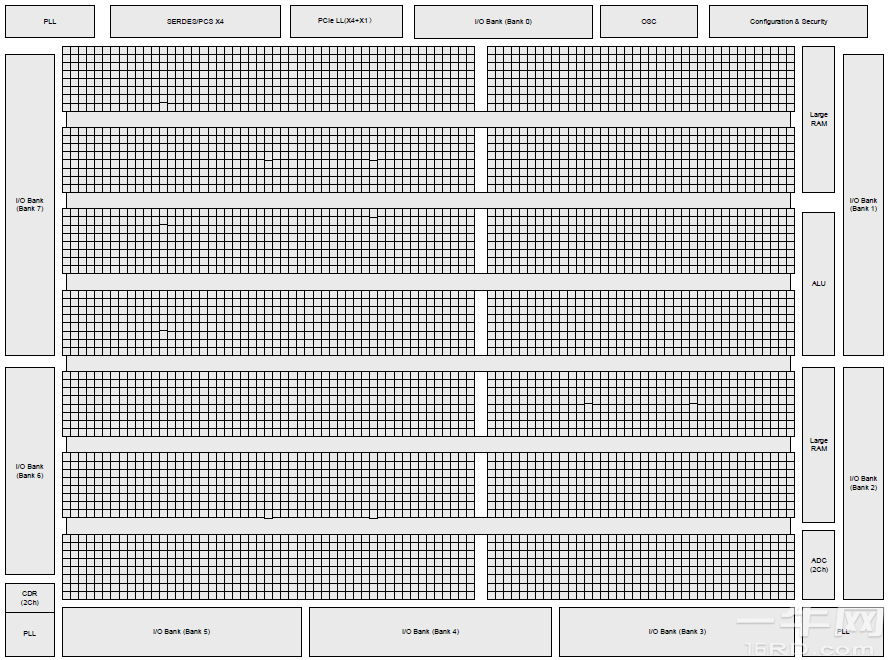

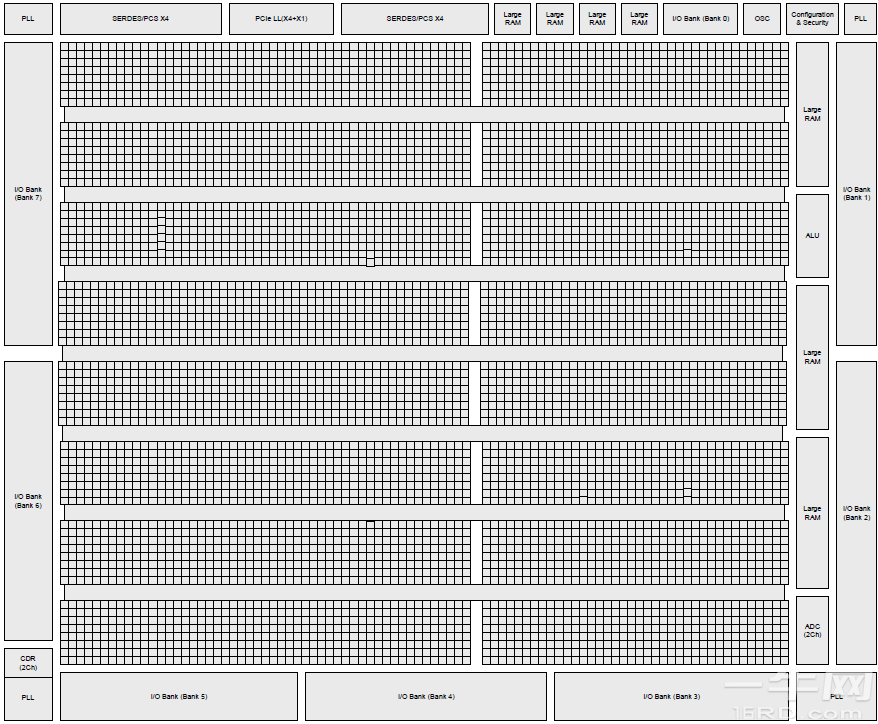

每个 CertusPro-NX 设备都包含一组被可编程 I/O 单元 (PIC) 包围的逻辑块。 散布在逻辑块行之间的是 sysMEM 嵌入式块 RAM (EBR) 行和 sysDSP 数字信号处理块行,如图 2.1 和图 2.2 所示。 例如,LFCPNX-100 器件具有三行 DSP 块和四行 sysMEM EBR 块。 此外,LFCPNX-100 器件包括七个大型 SRAM 块。 sysMEM EBR 块是大型专用 18 kbits 快速内存块,并具有内置 ECC 和 FIFO 支持。 每个 sysMEM 块都可以配置为具有各种深度和宽度的单个、伪双端口或真双端口存储器,如 RAM 或 ROM。 每个 DSP 模块支持多种乘法器和加法器配置,支持一个 108 位或两个 54 位累加器,它们是复杂信号处理功能的构建模块。

每个 PIC 块包含两个 PIO(PIO 对)及其各自的 sysI/O 缓冲区。 CertusPro-NX 设备的 sysI/O 缓冲区排列在八个组中,允许实施各种 I/O 标准。 位于器件顶部、左侧和右侧的宽范围 (WR) I/O bank 提供灵活范围的通用 I/O 配置,最高可达 3.3 V VCCIO。 位于器件底部的组专用于高性能 (HP) 接口,例如支持高达 1.8 V VCCIO 的 LVDS、MIPI、DDR3、LPDDR2、LPDDR3 和 LPDDR4。

可编程功能单元 (PFU) 包含用于逻辑、算术、RAM 和 ROM 功能的构建块。 PFU 块针对灵活性进行了优化,可以快速高效地实施复杂的设计。 逻辑块排列成二维阵列。 CertusPro-NX 设备中 PFU 和 sysI/O 块中的寄存器可以配置为 SET 或 RESET。 在加电和设备配置后,它根据用户设计进入用户模式,这些寄存器设置/重置,允许设备在已知状态加电以实现可预测的系统功能。

CertusPro-NX FPGA 具有多达八个嵌入式 10 Gbps SerDes 通道。 每个 SerDes 通道包含独立的 8b/10b 编码/解码、极性调整和弹性缓冲逻辑。 每组四个 SerDes 通道及其物理编码子层 (PCS) 块创建一个 Quad。 SerDes/PCS Quad 的功能可以在设备配置期间由 SRAM 单元设置控制,或者在设备操作期间由可寻址的寄存器控制。 每个 Quad 中的寄存器都可以通过莱迪思内存映射接口 (LMMI) 进行编程。 这些 Quad(最多两个)位于设备的顶部。 FPGA 还包括一个硬核 PCIe 链路层 IP 块,支持 PCIe Gen1、Gen2 和 Gen3。

此外,CertusPro-NX 设备提供各种系统级功能和接口硬核 IP,例如 I2C、SGMII/CDR 和 ADC 块。 CertusPro-NX 设备还提供安全功能,以帮助保护用户设计并通过提供增强的基于帧的 SED/SEC 功能提供更强大的可靠性。

提供的其他模块包括 PLL、DLL 和配置函数。 PLL 和 DLL 块位于每个设备的角落。 CertusPro-NX 设备还包括 LMMI,这是一个用于简单读写操作以控制内部 IP 的莱迪思标准接口。

系列中的每个器件都有一个 JTAG 端口。 该系列还提供片上振荡器和软错误检测 (SED) 功能。 CertusPro-NX 设备使用 1.0 V 作为其核心电压。

图 2.1。 简化框图,LFCPNX-50 器件(顶层)

图 2.2。 简化框图,LFCPNX-100 器件(顶层)

图 2.2。 简化框图,LFCPNX-100 器件(顶层)

2.2. PFU 块

CertusPro-NX 设备的核心由 PFU 块组成。 每个 PFU 块由编号为 0-3 的四个互连切片组成,如图 2.3 所示。 每个切片包含两个 LUT。 所有进出 PFU 块的互连都来自路由。

PFU 块可用于执行逻辑、算术、分布式 RAM 或 ROM 功能。 表 2.1 显示了每个片在分布式 SRAM 或非分布式 SRAM 模式下可以执行的功能。

|